# HERCROM400G2

# **Specification**

**CAL000**

**Ver 1.3**

# **CALYPSO**

**Department:** European Wireless Terminal Chipset Business Unit

|      | Originator          |

|------|---------------------|

| Name | Michel Gac          |

| Date | 25 - February- 2000 |

information are subject to change.

TI- Proprietary Information –

**PAGE: 1/51**

**Strictly Private**

UNDER NON DISCLOSURE AGREEMENT

# **HISTORY**

| Version | Date              | Author      | Approval manager           | Approval date | Notes |

|---------|-------------------|-------------|----------------------------|---------------|-------|

| 0.1     | 25 – Feb - 2000   | Michel Gac  |                            |               | 1,2   |

| 0.2     | 23 - May - 2000   | Michel Gac  |                            |               | 3     |

| 0.3     | 26 - June - 2000  | Michel Gac  |                            |               | 4     |

| 0.4     | 12 – July – 2000  | Michel Gac  | A.Boyadjian<br>L.Tannyeres | 16Aug-2000    | 5-6   |

| 0.5     | 10 – Augt- 2000   | Michel Gac  | L.Tannyeres                | 11Aug-2000    | 7     |

| 0.6     | 15 - Sept - 2000  | Michel Gac  | L.Tannyeres                | 19Oct-2000    | 8     |

| 0.7     | 26 – Jan – 2001   | Rodolphe S. | Michel Gac                 | 26jan-2001    | 9     |

| 0.8     | 22 – Mar – 2001   | Rodolphe S. | Michel Gac                 | 22mar-2001    | 10    |

| 0.9     | 3 – April – 2001  | Rodolphe S. | Michel Gac                 | 10Apr-2001    | 11    |

| 0.91    | 26 – April – 2001 | Rodolphe S. | Eric Balard                | 26Apr-2001    | 12    |

| 0.92    | 14 – May – 2001   | Rodolphe S. | Eric Balard                | 14May-2001    | 13    |

| 0.93    | 20 - Augt - 2001  | Rodolphe S. | Michel Gac                 | 21-Augt-2001  | 14    |

| 1.0     | 12 - Oct - 2001   | R. Servato  | Michel Gac                 | 15-Oct-2001   | 15    |

| 1.1     | 15 – Oct – 2001   | R. Servato  | Michel Gac                 | 14-Nov-2001   | 16    |

| 1.2     | 28- Nov -2001     | R. Servato  | Michel Gac                 | 28- Nov -2001 | 17    |

| 1.3     | 18 – June -2002   | R. Servato  | Michel Gac                 | 20-June-2002  | 18    |

# **Notes:**

- 1. Creation of document.

- Version derived from specification SAMS000 v1.7

- 3. Final ball-out assignment.

- Change MPU adress.

- 5. Updated §4.5.14, §4.5.22, §4.5.23, §4.5.24, §4.9

- 6. Updated connection figures

- 7. Fix bug in MPU paragraph.

- 8. Fix bug for KBC, DATA, TSPEN reset values.

- 9. Updated section 11.3: removed warning concerning GNA2 pin connexion.

- 10. Updated Table 6 INT4n, Update §11.3 (Ground name), remove §reference document, added restrication with NAUSICA usage

- 11. Update table 3 : Compatibility connection with Nausica, update Table 6 (remove pull up on nIBOOT)

- 12. Remove all wrong references document.

- 13. Add §10-Table8: PAD I/O Buffer type, update §3.5.21 MPU (minimum granularity of 8 bytes), update §3.5.22 DU, update §3.5.24 WRB.

- 14. Remove Pin EN\_LMM\_PWR in Ch 8 table Power management (wrong reference), update FIG 4 (1.8V instead of 1.4V)

- 15. update IOTA to power split DBB supply connections (ch 11.2.1.1)

- add features for C035: pin 140 nCS4: update Table 7&8, Update Ch 7.1(Memory interface using ADD(22), using CS4)

- 17. Improve lisibility for modifications done in previous version (Ch 8, 9, 10)

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

TI- Proprietary Information – PAGE: 2/51

Strictly Private

UNDER NON DISCLOSURE AGREEMENT

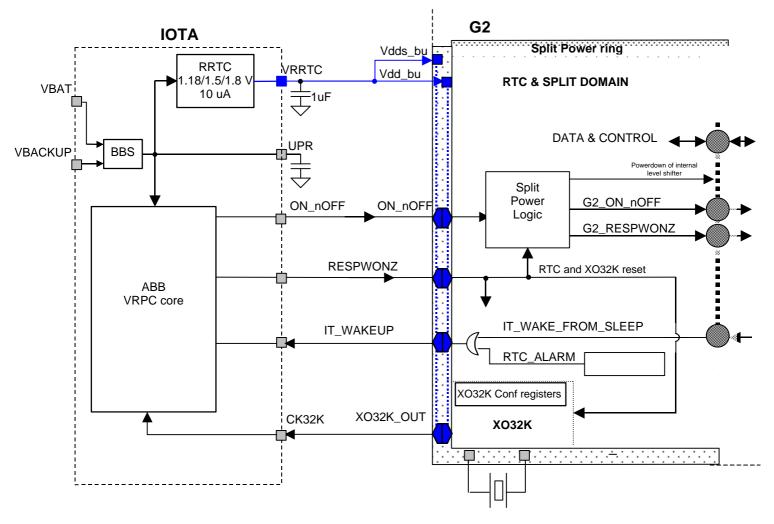

18. remove blank chapter 11.1 (Example of mobile terminal application), update IOTA to power split DBB supply connections figure (pin VLRTC=1.5v)

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI seems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI-products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Not does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1998, Texas Instruments Incorporated.

TI- Proprietary Information – PAGE: 4/51

# **SUMMARY**

| 1. | GLOSS            | ARY                                                          | 8  |

|----|------------------|--------------------------------------------------------------|----|

| 2. | GENER            | AL DESCRIPTION                                               | 9  |

| 3. | BLOCK            | SPECIFICATION                                                | 9  |

|    | 3.1 INT          | TRODUCTION                                                   | 9  |

|    |                  | M MEGACELL (ARM7TDMIE)                                       |    |

|    |                  | P SUBCHIP (S28C128)                                          |    |

|    | 3.4 CL0          | OCK SQUARER CELL                                             | 11 |

|    | 3.5 AR           | M PERIPHERALS                                                | 11 |

|    | 3.5.1            | Memory Interface                                             | 11 |

|    | 3.5.2            | Internal Static RAM                                          |    |

|    | 3.5.3            | Internal Boot Memory                                         |    |

|    | 3.5.4            | Die ID cell                                                  |    |

|    | 3.5.5            | Interrupt Handler (INTH).                                    |    |

|    | 3.5.6            | General purposes I/O (ARMI/O).                               |    |

|    | 3.5.7            | Micro Wire interfaces (UWIRE)                                |    |

|    | 3.5.8            | Timers (TIMER).                                              |    |

|    | 3.5.9            | IrDA Universal Async Receiver/transmitter 16C750 (UART-IRDA) |    |

|    | 3.5.10           | Universal Async Receiver/transmitter 16C750 (UART-MODEM)     |    |

|    | 3.5.11           | Subscriber Identity Module Interface (SIM)                   |    |

|    | 3.5.12           | Serial Port Interface (SPI)                                  |    |

|    | 3.5.13<br>3.5.14 | Time Processing Unit (TPU) Time Serial Port (TSP)            |    |

|    | 3.5.14<br>3.5.15 | Direct Memory Access controller (DMA)                        |    |

|    | 3.5.15<br>3.5.16 | Clock Management (CLKM)                                      |    |

|    | 3.5.17           | Pulse Width Tones (PWT)                                      |    |

|    | 3.5.17<br>3.5.18 | Pulse Width Light (PWL)                                      |    |

|    | 3.5.19           | Light Pulse Generator (LPG)                                  |    |

|    | 3.5.20           | I2C master serial interface (I2C)                            |    |

|    | 3.5.21           | Memory Protection Unit (MPU)                                 |    |

|    | 3.5.22           | Debug Unit (DU)                                              |    |

|    | 3.5.23           | GPRS Encryption Algorithm (GEA1-2)                           |    |

|    | 3.5.24           | Internal RAM write buffer (WRB)                              |    |

|    | 3.5.25           | Real Time Clock (RTC)                                        |    |

|    | 3.5.26           | Ultra Low-Power Down controller (ULPD)                       |    |

|    | 3.6 SPE          | CIFIC POWER-SPLIT FOR RTC                                    |    |

|    |                  | P PERIPHERALS                                                |    |

|    | 3.7.1            | Radio interface (RIF)                                        | 20 |

|    | 3.7.2            | Multi-Channel Serial Interface (MCSI)                        | 20 |

|    | 3.7.3            | Ciphering processor (CRYPT)                                  | 20 |

|    | 3.7.4            | Universal Asynchronous Receiver/transmitter (16C750)         | 20 |

|    | 3.7.5            | Direct Memory Access controller (DMA)                        | 20 |

|    | 3.7.6            | Interrupt Handler (INTH).                                    |    |

|    | 3.8 Gen          | NERAL PURPOSE PERIPHERALS                                    | 21 |

|    | 3.8.1            | JTAG                                                         |    |

|    | 3.8.2            | IDDQ                                                         |    |

|    |                  | OCK DIAGRAM                                                  |    |

| 4. | INITIA           | LIZATION PROTOCOL                                            | 22 |

|    |                  | RDWARE LOGIC RESET                                           |    |

|    | 4.2 AR           | M CODE DOWNLOADING                                           | 23 |

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

TI- Proprietary Information –

PAGE: 5/51

**Strictly Private**

UNDER NON DISCLOSURE AGREEMENT

| 4.3 DSP CODE EXECUTION         | 23         |

|--------------------------------|------------|

| 5. INTERRUPTS MANAGEMENT       | 24         |

| 5.1 DSP INTERRUPTS             | 24         |

|                                |            |

| 6. DMA MAPPING                 | 26         |

| 7. ADDRESS MAPPING             | 27         |

|                                |            |

|                                |            |

|                                | lt)27      |

| • •                            |            |

|                                |            |

|                                |            |

|                                |            |

|                                |            |

| 8. CALYPSO PINS DESCRIPTION    | 33         |

| 9. CALYPSO BALL-OUT            | 37         |

| 9.1 179GHH PACKAGE             |            |

| 10. PAD I/O BUFFER TYPE        | 42         |

| 11. APPLICATION EXAMPLE        | 46         |

| 11.1 POWER-SUPPLIES CONNECTION | 46         |

|                                | LYPSO      |

|                                | nections47 |

|                                | A ABB      |

|                                | 49         |

| 11.3 SIM CARD CONNECTION       | 50         |

| 11.4 KEYBOARD CONNECTION       | 51         |

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

**TI- Proprietary Information –**

**PAGE: 6/51**

**Strictly Private**

UNDER NON DISCLOSURE AGREEMENT

# **TABLE SUMMARY**

| TABLE 1: RESET MANAGEMENT                         | 23 |

|---------------------------------------------------|----|

| TABLE 2: DMA CHANNELS ALLOCATION                  | 26 |

| TABLE 3: ARM MEMORY SPACE                         | 29 |

| TABLE 4: ARM DATA FORMAT                          | 30 |

| TABLE 5: DSP XIO MEMORY SPACE                     | 32 |

| TABLE 6: CALYPSO PINS DESCRIPTION                 | 36 |

| TABLE 7: CALYPSO BALL MAPPING                     | 41 |

| TABLE 8: I/O BUFFER TYPE IN 179 BALLS VERSION     | 45 |

| TABLE 9: KEYBOARD SCANNING SEQUENCE               | 51 |

|                                                   |    |

| FIGURE SUMMARY                                    |    |

| FIGURE 1: CALYPSO INTERNAL ARCHITECTURE           |    |

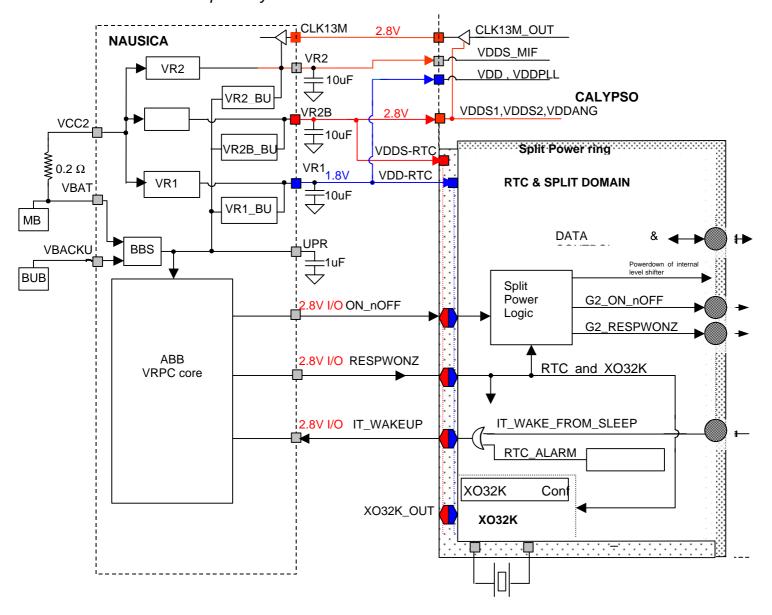

| FIGURE 3: COMPATIBILITY CONNECTION WITH NAUSICA   |    |

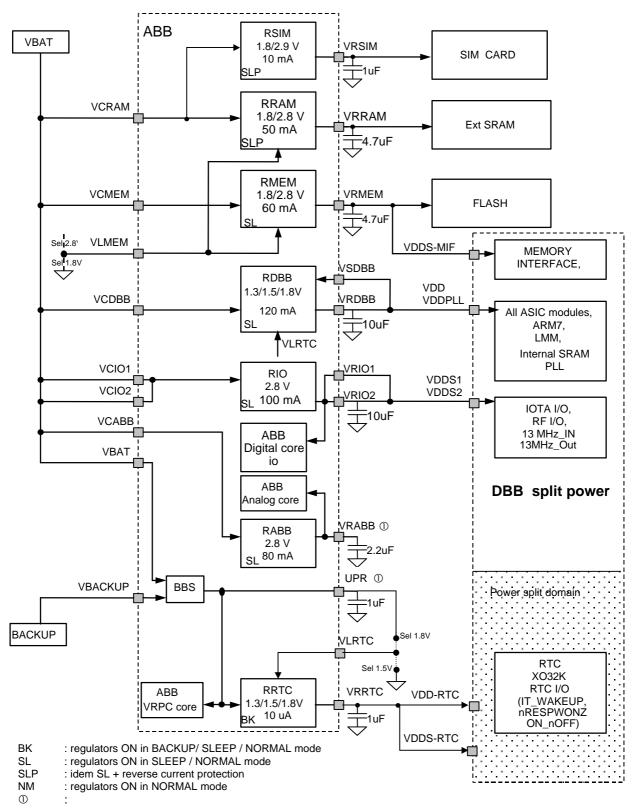

| FIGURE 4: POWER SUPPLIES CONNECTION WITH IOTA ABB |    |

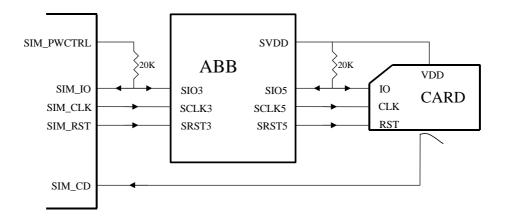

| FIGURE 5: SIM CARD CONNECTION                     | 50 |

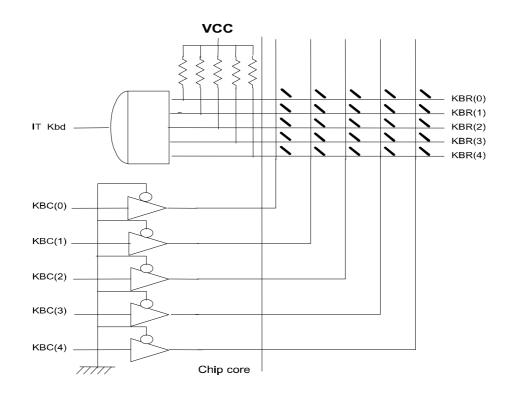

| FIGURE 6: KEYBOARD CONNECTION                     | 51 |

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

TI- Proprietary Information –

**Strictly Private**

UNDER NON DISCLOSURE AGREEMENT

DO NOT COPY

**PAGE: 7/51**

#### 1. GLOSSARY

APIF: Arm Port InterFace.

BGA: Ball Grid Array.

CLOCK M: CLOCK Managment.

CPU: Central Processor Unit

DAI: Digital Audio Interface

DSP: Digital Signal Processor.

FLASH: Flash E2prom

GSM: Global System for Mobile communications.

HPI: Host Port Interface.

H/W: **H**ard**W**are.

INTH: INTerrupt Handler.

ISO: International Standards Organization

I/O: Input / Output.

JTAG: Joined Test Action Group

MxxLyy Mega-module **DSP** with xx RAM and yy ROM.

LCD: Liquid Cristal Display

LMM: DSP Mega-Module

MCU: Micro-Controller Unit.

MCSI: Multi Channels Serial Interface

MEM INT: MEMory INTerface.

P.C.: Personal Computer

PMT: Parallel Multiplexing Test.

PLL: Phase Loop Lock

RIF: Radio Interface Function.

RISC: Reduced Instruction Set Computer

RAM: Random Access Memory

ROM: Read Only Memory

SIM: Subscriber Identity Module.

S/W: **S**oft**W**are.

TDMA: Time Division Multiple Access.

TPU: Time Processing Unit.

TQFP: Thin Quad Flat Pack.

TSP: Time Serial Port.

USART: Universal Synchronous/Asynchronous Receiver Transmitter

USB: Universal Serial Bus RTC: Real Time Clock

ULPD: Ultra Low Power Device

BIST: Built In Self Test LPG: Led Pulse Generator

PWL: Pseudo-noise pulse Width Light modulator

PWT: Pulse Width Tone generator

I2C: Inter IC Control

#### 2. GENERAL DESCRIPTION

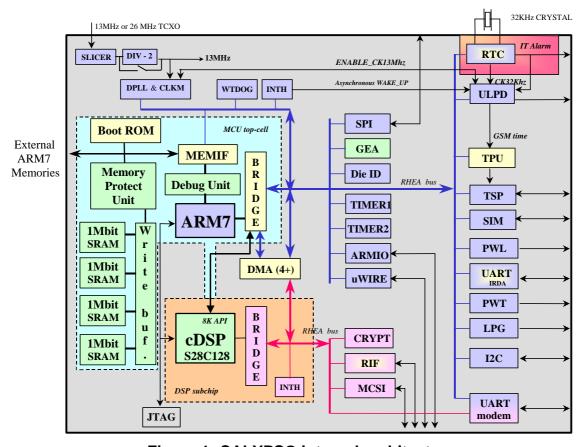

CALYPSO is a chip implementing the digital base-band processes of a GSM/GPRS mobile phone. This chip combines a DSP sub-chip (LEAD2 CPU) with its program and data memories, a Micro-Controller core with emulation facilities (ARM7TDMIE), internal 8Kb of Boot ROM memory, 4M bit SRAM memory, a clock squarer cell, several compiled single-port or 2-ports RAM and CMOS gates.

The application of this circuit is the management of the GSM/GPRS base-band processes through the GSM layer 1, 2 and 3 protocols as described in the ETSI standard with a specific attention to the power consumption in both GSM dedicated and idle modes, and GPRS (class 12) capability.

The chip will fully support the GSM full-level test approval (FTA) for both Full-Rate, Enhanced Full-Rate and Half-Rate speech coding.

CALYPSO implements all features for the structural test of the logic (full-SCAN, BIST, PMT, JTAG boundary-SCAN).

#### 3. BLOCK SPECIFICATION

#### 3.1 INTRODUCTION

CALYPSO architecture is based on two processor cores ARM7 and LEAD2 using the generic TI RHEA bus standard as interface with their associated application peripherals. CALYPSO is composed from the following blocks:

ARM7TDMIE

ARM7TDMI CPU core (32/16 bits RISC processor)

- + ARM ice crusher for emulation purpose

- DSP subchip S28C128

LEAD2 DSP core with 28K words of RAM and 128K words of ROM

- + API (8 Kw part of the 28K of RAM)

- + SPI

- + TIMER

- Clock Squarer analog cell.

- ARM peripherals:

#### General purpose peripherals

- ARM Memory Interface for external RAM, Flash or ROM

- RHEA bridge

- 4 Mbit Static RAM with write-buffer

- Memory Protection Unit (MPU)

- Debug Unit (DU)

- 64 Kbit of via2-ROM for internal boot.

- Die-ID cell (48 bits + 5 spare).

#### Application peripherals

- ARM General purposes I/O with keyboard interface and two PWM modulation signals for light and buzzer with possible tones generation.

- Micro Wire interfaces for LCD and EEPROM.

- 3 Timers (generic, watchdog)

- UART 16C750 interface (UART\_IRDA) with

- IRDA control capabilities (SIR)

- Software flow control (UART mode).

- hardware flow protocol (DCD, CTS/RTS)

- UART 16C750 interface (UART MODEM) with

- hardware flow protocol (DCD, CTS/RTS)

- autobaud function

- SIM Interface.

TI- Proprietary Information –

PAGE: 9/51

**Strictly Private**

UNDER NON DISCLOSURE AGREEMENT

- ARM interrupts Handler (INTH).

- GSM real-time sequencer (TPU).

- GSM real-time Serial Port (TSP).

- DMA controller (4 channels 2 ports)

- Real Time Clock (RTC)

- GSM Ultra Low-Power Device (ULPD)

- Clock generator & control with Digital Phase Locked Loop (CLKM)

- Programmable controller for Led pulse generation (LPG)

- Enhanced tone generator (PWT)

- Pseudo-noise modulator for light level control (PWL)

- Master I2C serial interface

- GPRS Encryption Algorithm module 1 & 2.

- ASIC DSP peripheral:

#### General purpose peripherals

RHEA bridge

# Application peripherals

- Radio interface (RIF).

- Multi Channels Serial Interface (MCSI).

- A51/A52 ciphering (CRYPT)

- UART 16C750 interface (UART\_MODEM) with

- hardware flow protocol (DCD, CTS/RTS)

- autobaud function, local echo.

- DMA controller (4 channels)

- DSP interrupts Handler (INTH).

- OTHER ASIC peripherals.

- JTAG TAP controller.

#### 3.2 ARM megacell (ARM7TDMIE)

The ARM7TDMI is a 32 bits RISC micro-controller core. This microprocessor work in 32 bits or 16 bit instructions and on 32, 16 or 8 bit data. The ARM7 architecture is based on reduced instruction set computer (RISC). Pipelining is employed so that all parts of the processing and memory systems can operate continuously. Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory. In CALYPSO chips family, ARM7 is intended to work in 'little endian' mode only.

The CPU is associated with an emulation module called IceCrusher, which provides many debug functions:

- Single processor and multiprocessor debug.

- High level language and assembly debug (Run, Halt, Step...).

- Real Time (CPU continuously running) or Non real-time (CPU stopped) debugs options.

- Combined 32 and 16 bit mode for ARM processor.

- Endianess transparency.

- Unlimited breakpoints via op-code replacement (S/W breakpoint).

- 2 Hardware breakpoints (one configurable as SW breakpoint) with maskable cycle type, address and data compare.

- 2 external breakpoint events.

- Internal events generate external triggers.

- Benchmarking / profiling capability.

and is issued for evaluation purposes only.

information are subject to change.

Strictly Private

TI- Proprietary Information –

**UNDER NON DISCLOSURE AGREEMENT**

DO NOT COPY

PAGE: 10/51

## 3.3 DSP subchip (S28C128)

The DSP subchip is a Digital Signal Processor core compliant with the TMS320C54x family. The CPU core LEAD2 is associated with a ARM Port Interface (API), an interrupt handler, a parallel interface XIO, a Timer, 28K words of RAM including 8K words of API shared memory, 128K words of ROM, a serial port, and a JTAG interface.

The input clock frequency is delivered by an external DPLL and the functional cycle frequency is planned to be in the range [0 - 91 MHz].

# 3.4 Clock Squarer cell

The Clock Squarer cell is an analog cell which function is to reshape a clock signal provided by an external oscillator. The input signal is assumed to be a pseudo-sinusoidal signal with a limited dynamic transformed by the Clock Squarer cell in a square waveform with an amplitude of VCC (see electrical characteristics of signal CLKIN in Appendix B).

## 3.5 ARM peripherals

# 3.5.1 Memory Interface.

The Arm memory interface handles:

- External ARM memory access management: It performs

- ⇒ ARM read and write access size adaptation to the memory width (from 8-bit up to 32-bit).

- ⇒ ARM access duration management (wait state insertion or using 'nREADY' input) to enable the connection of slow memory devices.

- ⇒ Memory control signals generation (chip-selects, write strobe generation,...) with up to 4 chip-select signals corresponding each to an address range of 8 Mbytes.

#### ARM to API memory access management:

- ⇒ ARM access size adaptation for API read and writes access. A 32-bit API READ transaction is transformed into 2 16-bit read access. A 32-bit API WRITE access is transformed into 2 16-bit write transaction.

- ⇒ Address signal-timing adaptation to be compliant with the API interface requirement.

#### • ARM to Rhea bridge access management:

- ⇒ ARM accesses size adaptation for Rhea accesses. The access size adaptation is done regarding the Rhea peripheral minimal transaction size. If the Rhea peripheral can not handle byte transaction, then no byte write transaction can be done.

- ARM nWAIT and access control flags generation (byte-latch, etc...).

#### 3.5.2 Internal Static RAM

Four megabit of static RAM (SRAM) are embedded on the die and mapped on nCS6 chip-select of the memory interface. These memories can be read or written either in 8, 16 or 32 bits format. The access cycle is guaranteed with 0 wait-state for any cycle frequency up to fmax MHz.

information are subject to change.

TI- Proprietary Information – PAGE: 11/51

## 3.5.3 Internal Boot Memory

A 64Kbit ROM is embedded and mapped on nCS7 chip-select of the memory interface. This memory can be read either in 8, 16 or 32 bits format. The access cycle is guaranteed with 0 wait-state for any cycle frequency up to fmax MHz.

Depending of the state of the nIBOOT signal, this memory is mapped on nCS0 or nCS7, to allow the CPU to boot (at reset) on external or internal memory.

#### 3.5.4 Die ID cell

The Die ID cell is a 64-bit register composed of fuse cells programmed by Laser during fabrication process. Each Die ID is unique.

See chapter 16.4.

# 3.5.5 Interrupt Handler (INTH).

The interrupt handler provides 21 prioritized and maskable interrupts to the ARM core.

It receives interrupts from both internal modules and external chip environment. Each incoming interrupt is configured as a low level sensitive or falling edge sensitive interrupt and can be individually masked using dedicated configuration registers.

An Interrupt Level Register is associated to each incoming interrupt to define a priority to the corresponding interrupt. If several interrupts have the same priority level, they are sent in a predefined order.

Each interrupt can be routed to one of the two input interrupts of the ARM core FIQ (Fast Interrupt request) and IRQ (Low priority Interrupt request).

# 3.5.6 General purposes I/O (ARMI/O).

We provide fifteen I/O pins configurable in read or write mode by internal registers.

10 special I/O pins are dedicated for keyboard connection: 5 output (Columns) and 5 input (Rows). The five input pins are connected on 1 interruption for wake-up mode.

A Pulse Width Modulated pin is dedicated to the control of the buzzer. A dedicated timer is used to generate the waveform shape, which modulates the buzzer PWM signal thus producing tones in the human audible spectrum.

## 3.5.7 Micro Wire interfaces (UWIRE).

This serial interface can drive external devices as serial EEPROM or LCD with 2 chip-selects with respect to the micro wire standard.

The serial clock period is derived from the reference 13MHz clock and can be configured as:  $T_{SCLK} = CK\_FREQ * Csi\_FRQ * T_{13M} = [2/4/7/10] * [2/4/8] * T_{13M}$

<u>Note</u>: the use of the uWIRE interface is exclusive with the use of the I2C interface (same I/O pins).

information are subject to change.

TI- Proprietary Information – PAGE: 12/51

## 3.5.8 Timers (TIMER).

The chip implements three 16 bits timers configurable either in 'auto reload' or in 'one shot' modes. The timers generate interrupts to the ARM when equal to zero.

The first timer is configured by default as a Watchdog for the MCU. If a programmer doesn't want to have this functionality, he must write a specific sequence into a dedicated register in order to configure it as a general-purpose timer.

The two other timers are general-purpose timers.

# 3.5.9 IrDA Universal Async Receiver/transmitter 16C750 (UART-IRDA).

This UART interface is compatible with 16C750 compliant devices. It includes the Slow Infra Red protocol in order to be connected with an infrared transmitter to any external data peripherals with an IrDA compliant data interface.

The IR function can be disabled and the UART connected through a standard wired interface. This UART is primarily intended to be linked with the modem of an external PC for concurrent debugging purpose.

The module integrates two 64 words (9 and 11 bits) receive and transmit FIFO and one 8 words (8 bits) status FIFO (IrDA only) which trigger levels are programmable. The baud-rate is internally generated from a programmable divisor.

Transmission parity can be even, odd, none and the number of stop bits is 1, 1.5 or 2.

The receiver can detect break, idle or framing errors, and FIFO overflow and parity errors.

The transmitter can detect FIFO underflow.

All modem operations are controllable via a software interface.

In IrDA mode, this upgraded UART 16C750 includes the following additional features:

- IrDA 1.0 SIR support allows serial communication at baud rates up to 115.2 kbaud.

- Pulse shaping, and pulse recovering. Sending a single infrared pulse signals a zero. A one

is signaled by not sending any pulse. The width of the pulse can be either 1.6 us or 3/16<sup>th</sup> of

a single bit time.

- The device operation, in IrDA 1.0 SIR, is similar to the operation in UART mode. The main difference being that the data transfer operations are normally performed in half-duplex, the modem control and status signals are not used.

- Frame formatting: addition of variable xBOF characters and EOF characters

- Uplink/downlink CRC generation/detection

- Asynchronous transparency (automatic insertion of break character)

- 8 characters status FIFO available to monitor frames length and frame errors.

- Variable frame length for RX and TX IrDA frame.

**Note**: MIR and FIR are not implemented.

TI- Proprietary Information – PAGE: 13/51

## 3.5.10 Universal Async Receiver/transmitter 16C750 (UART-MODEM)

This UART interface is compatible with the NS 16C750 device.

This UART 16C750 is devoted to the connection to a Modem through a standard wired interface.

The module integrates two 64 words (9 and 11 bits) receive and transmit FIFOs which trigger levels are programmable. The baud-rate is internally generated from a programmable divisor. Transmission parity can be even, odd, or none and the number of stop bits is either1, 1.5 or 2. The receiver can detect break, idle or framing errors, FIFO overflow and parity errors. The transmitter can detect FIFO underflow.

All modem operations are controllable either via a software interface or using hardware flow control signals.

This upgraded UART 16C750 includes the following additional features:

- Hardware flow control (DCD, RTS/CTS)

- Auto-bauding with the possibility to match to baud-rate from 1200 to 115.2Kbits/s.

This UART is shared between the ARM7 and the DSP processors. One processor only at a time can controlled the UART. The allocation of the UART is defined by the ARM7 (configuration register). By default, the UART is connected to the ARM7 RHEA bus.

## 3.5.11 Subscriber Identity Module Interface (SIM).

The Subscriber Identity Module interface will be fully compliant with the GSM 11.11 and ISO/IEC 7816-3 standards.

Its external interface is 3 Volts only. 5 Volts adaptation will be based on external level shifters. The SIM interface supports the cold and warm reset procedures and the disabling of the clock (static SIM cards).

#### 3.5.12 Serial Port Interface (SPI)

The SPI is a full-duplex serial port configurable from 1 to 32 bits and provides 3 enable signals programmable either as positive or negative edge or level sensitive.

The serial clock period is derived from the reference 13MHz clock and can be configured as:  $T_{MCUCLK} = PTV * T_{13M} = [1/2/4/8/16] * T_{13M}$

#### 3.5.13 Time Processing Unit (TPU)

The TPU is a real-time sequencer dedicated to the monitoring of GSM base-band processing's. Working from an event table referring to a GSM TDMA time base, the TPU activates tasks to control DSP peripherals with respect of the time constraints related to the GSM sequencing. To store the real-time microinstructions of the sequencer, the TPU includes one 2 ports RAM of 1024 words of 16 bits with a dual page addressing capability.

MCU could access at the full RAM in write mode only when TPU is running.

TI- Proprietary Information – PAGE: 14/51

#### 3.5.14 Time Serial Port (TSP)

The TSP is a peripheral of the TPU, which includes both a serial port (32 bits) and a parallel interface. The serial port can be programmed by the TPU with a time accuracy of the guarter of GSM bit. The serial port is uni-directional (transmit only) when used with NAUSICA but can be configured in bi-directional to keep compliant with VEGA3. The serial ports provide 4 enable signals programmable either as positive or negative edge or level sensitive.

The parallel interface allows controlling 13 external individual output and 1 internal signal with a time accuracy of the quarter of GSM bit.

These parallel output signals are mainly used to control the RF activity.

The single internal signal is looped on one interrupt line of the DSP in order to offer a possibility of sequencing the DSP tasks scheduling on a quarter of GSM bit time accurate event.

The serial clock frequency is fixed to 6.5MHz.

#### 3.5.15 Direct Memory Access controller (DMA)

The DMA controller manages data transfers between the RHEA peripherals and the DSP API memory. The main features are:

- Four independent DMA channels

- Configuration of channels from the MCU only (master, direction)

- Either the DSP or the ARM host can control each DMA channel

- All DMA transactions are using the ARM Rhea bus

- The DMA transaction width can be either 8 or 16-bit data

- Unknown transfer length support and double-page destination buffers

#### 3.5.16 Clock Management (CLKM)

This module is in charge of the control of the clock activity for the DSP, MCU and RHEA peripherals. It includes one DPLL and configuration register for DSP and MCU clocks frequencies programming.

CLKM manages also the reset of all modules connected either to the MCU Rhea bus or the DSP Rhea bus and the scheduling of the deep power of the external FLASH memory.

The DPLL is programmable in "multiplication-mode" with the following values:

$$F_{out} = F_{in} \times \frac{m}{d}$$

m = 1 up-to 32 (step 1) d = 1, 2, 3 or 4

It could be also programmable in "division-Mode" with the following:

$$F_{out} = \frac{F_{in}}{k}$$

k = 1, 2 or 4

#### 3.5.17 Pulse Width Tones (PWT)

This module generates a modulated frequency signal for the external buzzer. Frequency is programmable between 349Hz and 5276Hz with 12 half tone frequencies per octave. The volume is also programmable.

Features characteristic data and other information are subject to change.

Strictly Private

TI- Proprietary Information –

**UNDER NON DISCLOSURE AGREEMENT**

DO NOT COPY

PAGE: 15/51

# 3.5.18 Pulse Width Light (PWL)

This module allows the control of the backlight of LCD and keypad by employing a 4096bit random sequence. This voltage level control technique decreases the spectral power at the modulator harmonic frequencies. The block uses a switchable clock of 32kHz, independent of UPS.

# 3.5.19 Light Pulse Generator (LPG)

This peripheral produces the signal for the blinking LED. Blink period and duration are programmable.

# 3.5.20 I2C master serial interface (I2C)

The I2C is a half-duplex serial port using 2 lines (data and clock) for data transmission with software addressable external devices. The interface is compliant with the Philips standard. The main features of the interface are:

- single master only

- standard (100KHz) and the fast (400KHz) transmission modes

- support both burst write, single read and combined read modes

- transmit burst buffer of 16 words

- 3 bits programmable spike filtering logic

- error handling capability during I2C bus access

<u>Note:</u> the use of the I2C interface is exclusive with the use of the uWIRE interface (same I/O pins).

#### 3.5.21 Memory Protection Unit (MPU)

Within a memory space, the MPU allows defining memory sub-regions, each having a separate Read/Write protection attribute; this permits for partitioning the memory space into program instruction, system data, user data, stack ...

The application program configures the MPU, which interfaces to the processor via the RHEA bus. The address bus directly issued from the processor is monitored providing a real-time position of the memory region accessed. When a protection breach attempt occurs, the memory control signals are affected, not selecting the memory, and the fault condition is indicated to the processor.

The MPU allows for controlling:

- Up to four programmable protected regions within a memory space of 512 Kbyte.

- A maximum protected size of 128 Kbyte for each region (512 Kbyte for 4 regions).

- A minimum granularity of 8 bytes.

- A privileged-code memory region.

For each region, memory mapped control registers define:

- Protected memory region base-address.

- Starting/ending addresses within the protected memory region.

- Protection mode (Non-User R/W, User Read-only, ROM, Privileged-region write...

-see Protection Mode definition-) applied to the memory sub-region bounded by the starting/ending addresses.

- Out-of-protection (upper-bound) indication enabled/disabled.

Features characteristic data and other information are subject to change.

TI- Proprietary Information – PAGE: 16/51

Strictly Private

UNDER NON DISCLOSURE AGREEMENT

The MPU generates:

- An illegal-access signal if the application program attempts a non-authorized access to a memory region (i.e. User write access to a region programmed for User Read-only accesses).

- An Out-of-protection signal when the application program attempts to read or write

to a location within a memory region (defined by the base-address) and above the

upper limit (end-address) of the protected sub-region. (helpful for stack

overflow/under-flow monitoring).

- A MPU-fault signal which is the OR'ed combination of both Illegal-access and Outof-protection signals.

- A fault indication (Illegal-access and/or Out-of-protection) flagged into the MPU status register which is available to the processor for fault analyze.

# 3.5.22 **Debug Unit (DU)**

The Debug Unit is a hardware resource intended to provide additional support to a software abort-handler. The DU provides *64* stages deep history table of the last memory accesses prior entering the abort mode, then permitting analysis of previous bus transaction's.

The DU is an autonomous function that does not need to be configured, hence, does not interfaces to a control bus such as RHEA. The DU is connected directly to the processor busses (Address & Control) from where it collects the data, and to the memory interface system where the saved history table can be read.

The Debug Unit offers the following:

- Sixty-four 32-bit words deep FIFO register file

- 26-bit Processor Address and 8 Processor control signals recorded (nM[1:0], MAS[1:0], nEXEC, nOPC, nMREQ, nRW)

- Continuous storage for every processor fetch (either instruction or data)

- Data record automatically frozen upon switch to abort mode

- Memory-like read access during abort operating mode

- Enable/disable control from input module pin (typically connected to a chipconfiguration register-bit).

- General purpose RAM when debug function is disabled.

#### 3.5.23 GPRS Encryption Algorithm (GEA1-2)

In GPRS mode, the data confidentiality is performed by a ciphering function (GPRS Encryption Algorithm). The ciphering is executed within the LLC upper layer. According to the option negotiated with the network the GEA mode 1 or mode 2 may be selected.

The purpose of the LLC is to convey information between the mobile station and the Serving GPRS Support Node. The procedures used are modeled upon the HDLC concepts. The LLC shall support both acknowledge and unacknowledged mode and implement a FCS according to the mode used.

The HW block provided support the computation of the FCS according to the LLC frame to send/received as well as the ciphering/deciphering GEA mode 1 and 2. These procedures are described in 01.61, 04.64 GSM recommendations and detailed in GSM MoU documents.

#### 3.5.24 Internal RAM write buffer (WRB)

The write buffer increases the speed of memory accesses, thanks to write pipe mechanism. (The idea is to allow a complete CPU cycle time for read access).

information are subject to change.

TI- Proprietary Information – PAGE: 17/51

# 3.5.25 Real Time Clock (RTC)

The RTC block is an embedded Real Time Clock module, directly accessible from RHEA bus interface.

Its basic functions are:

- Time information (seconds/minutes/hours) coded in BCD

- Calendar Information (Day/Month/Year/ Day of the week) directly in BCD code up to year 2099

- Alarm function with interrupts generation based on a periodical (second/minute/hour/day) or a precise time event in the century (second accuracy).

- 30s time range correction

- 32KHz oscillator frequency gauging.

# 3.5.26 Ultra Low-Power Down controller (ULPD)

The ULPD block is used for the DEEP SLEEP MODE management. It allows stopping the accurate 13MHz VTCXO during the discontinuous reception phases in GSM idle mode in order to save power consumption. Moreover, the ULPD sequencer is used to monitor the chip activity in terminal OFF mode, thus deriving the original GSM Deep Sleep mode concept to the whole terminal activity.

The main functions of the ULPD block are:

- gauging of the 32 kHz quartz based oscillator

- maintenance of GSM time during deep sleep mode with the minimum time accuracy to allow a burst demodulation at wake-up

- programmable timer to exit deep sleep mode

- delivery of the 13MHz master to the CLKM module

- switching between 13MHz and 32KHz

- generation of chip functional reset

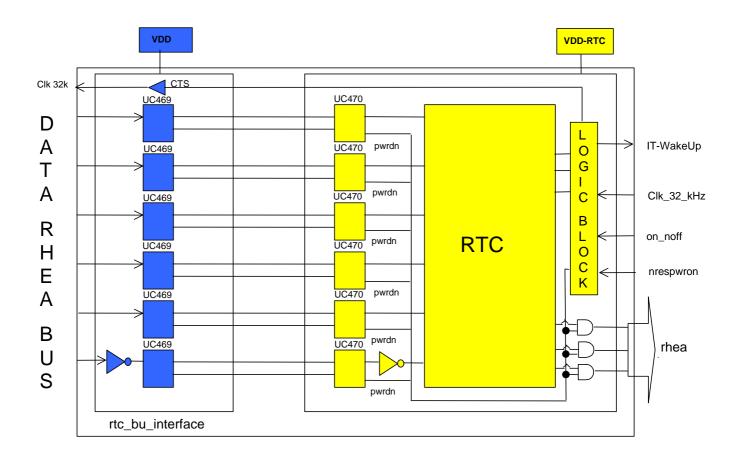

# 3.6 Specific power-split for RTC

To have a minimum of consumption in mobile equipment, only the active logic elements have to be supplied. This approach is possible by using Split Power.

It consists by the use of Tactical Cells to split the core power domain in two sub domains powered with different voltage supplies.

The separation between the core and the active domain is realized by Tactical cells and more precisely by Internal Level Shifters. The Internal Level Shifters (ILS) are library standard macrocells to interface two core domains with two different supplies.

When the core domain is unknown, these cells have a Power-Down signal, which allows to set the output of the ILS to 0 and to have any through current. So ILS are going to be placed on each wire between the active elements and the core.

The aim of the Split Power is to have a minimum of consumption in OFF state. For a mobile the only necessary element to supply in OFF is the RTC. So the tactical cells will be placed to isolate the RTC.

To use the Split Power, Calypso had to have pins VDDRTC, VDDSRTC, VSSRTC as specific power-supplies for both core and IOs.

The pin which are going to be suplied with specific power supplies are :

| - | ON/OFF     | (in)      |

|---|------------|-----------|

| - | NRESPWRON  | (in)      |

| - | IT_WAKEUP  | (out)     |

| - | CLK32K_OUT | (out)     |

| - | OSC32K_IN  | (Xtal in) |

| _ | OSC32K OUT | (Xtal out |

Features characteristic data and other information are subject to change.

TI- Proprietary Information –

Strictly Private

PAGE: 18/51

## 3.7 DSP peripherals

# 3.7.1 Radio interface (RIF)

The RIF (Radio Interface) Module is a buffered serial port derived from the BSP peripheral module of the defined for TMS320C5X

The external serial data transmission is supported by a full-duplex double buffered serial port interface.

The DSP exchanges data with the RIF through either its

- -XIO interface for configuration data and radio data in word by word protocol or its

- API interface for radio data in DMA mode (buffered mode with data block transfer)

For each data transfer between DSP and RIF, an interrupt is sent to DSP (XIO mode) or a DMA request and an 'end-DMA' request is sent to ARM.

Transmit serial clock is either generated internally or externally. Receive serial clock is always generated externally.

The RIF uses an internal 13MHz clock to manage the auto-buffering function.

# 3.7.2 Multi-Channel Serial Interface (MCSI)

The MCSI is a serial interface supporting both single and multi-channels (x16) communications. Words length, frame format, baud-rates are fully programmable.

The interface can be additionally configured to support GSM DAI test mode with the possibility to synchronize DAI with the voice frame signal.

# 3.7.3 Ciphering processor (CRYPT)

The ciphering processor implements both A51 and A52 algorithms as defined in GSM Rec03.20 and detailed in GSM MoU documents.

# 3.7.4 Universal Asynchronous Receiver/transmitter (16C750)

UART interface compatible with the NS 16C750 device.

This UART is shared between the ARM7 and the DSP processors. One processor only at a time can control the UART. The ARM7 configuration register defines the allocation of the UART). By default, the UART is connected to the ARM7 RHEA bus.

#### 3.7.5 Direct Memory Access controller (DMA)

The DMA module is shared between DSP and MCU processors. The DMA have only two port DSP-API memory and MCU-RHEA, so it allows RHEA peripheral to use DMA channel between us and the API memory.

information are subject to change.

TI- Proprietary Information – PAGE: 20/51

# 3.7.6 Interrupt Handler (INTH).

The interrupt handler provides 21 interrupts to the DSP core.

It receives interrupts from both internal modules and external chip environment. Each incoming interrupt is configured as a low level sensitive or falling edge sensitive interrupt. The mask and the interruption level of the interrupts are configured in the DSP core itself.

# 3.8 General purpose peripherals

#### 3.8.1 JTAG

The JTAG interface (TAP) of the chip can be selected either

to access the 2 processors on-chip emulators with a pseudo IEEE JTAG protocol for emulation purposes. A PC or workstation can be connected to the interface to set the biemulation mode with the ARM core linked to DSP core. The IceCrusher module supports the synchronization between the 2 cores.

Or

To dialog with an embedded TAP controller which instructions set support all the IEEE 1149 BSCAN modes, the programming of the chip I/Os configuration (PMT modes, full-scan modes, BIST modes, functional 1 or 2 modes) and the selection of the boundary-scan chain for FLASH EPROM programming.

#### 3.8.2 IDDQ

Pulling high the IDDQ pin sets the IDDQ configuration.

In IDDQ mode, all analog devices are disabled thus allowing reducing the chip current consumption to the single leakage currents. Moreover, a direct control of the ARM and DSP resets and clocks is allowed through, respectively, the pin BCLKR and CLKTCXO of the chip.

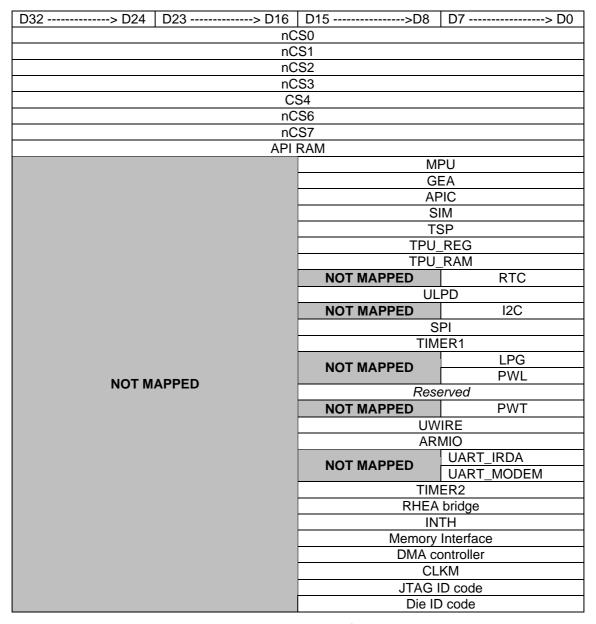

# 3.9 Block Diagram

Figure 1: CALYPSO internal architecture

# 4. INITIALIZATION PROTOCOL

#### 4.1 Hardware logic reset

The chip receives one external reset signal (active low):

\* The power-on reset (nRESPWRON) initializes the whole digital logic devices. It is activated each time the power supply is applied to the chip.

The functional reset is generated internally from the ULPD controller:

\* The internal functional reset (nRESET) initializes the logic devices working on any clocks derived from the 13MHz-clock reference or the processor strobes. This reset is activated each time the terminal is switched in OFF mode and maintained active as long as the external control pin ON\_nOFF is at low level.

Internally to the chip, three reset signals are provided in order to dissociate the reset of the logic working on the 32KHz or TCK clocks and the reset of the logic working on clocks derived from the reference clock 13MHz or the processors strobes. Namely:

- nRESET\_32K ⇒ JTAG, RTC and ULPD modules.

- nRESET\_DSP ⇒ all logic mapped on the DSP Rhea bus except 32KHz based logic

- nRESET\_MCU ⇒ all logic mapped on the MCU Rhea bus except 32KHz based logic

Externally to the chip, two reset signals can be controlled by the MCU to reset selectively external components and to control the deep power mode of external FLASH memories

- nRESET\_OUT ⇒ external components.

- FDP ⇒ FLASH deep power (reset delay controlled with CNTL\_ARM\_CLK (deep\_power).

|                     |            | Reset signal |            |            |     |  |  |  |

|---------------------|------------|--------------|------------|------------|-----|--|--|--|

| Control             | nRESET_32K | NRESET_DSP   | nRESET_MCU | nRESET_OUT | FDP |  |  |  |

| NRESPWRON           | Yes        | Yes          | Yes        | Yes        | Yes |  |  |  |

| NRESET              | No         | Yes          | Yes        | Yes        | Yes |  |  |  |

| RST_CMD watchdog    | No         | Yes          | Yes        | No         | Yes |  |  |  |

| CNTL_RST(DSP_reset) | No         | Yes          | No         | No         | No  |  |  |  |

| CNTL_RST(ext_reset) | No         | No           | No         | Yes        | No  |  |  |  |

**Table 1: Reset management**

After ARM reset the ARM program counter point to 0000:0000 address. After DSP reset the DSP program counter point to 0000:FF80 address.

Each module implements in its control register a software-reset bit, which can be activated by its master processor. By default, these bits are set as soon as the processor reset (nRESET\_DSP or nRESET\_DSP) is activated.

#### 4.2 ARM code downloading

In debug mode, when external Ram is used to replace FLASH or ROM, the program code is downloaded thanks to JTAG facilities. Flash memory program is downloaded through the JTAG TAP using the dedicated boundary-scan chain.

ROM or EPROM devices must be programmed before assembly.

#### 4.3 DSP code execution

When releasing the DSP reset signal nRESET\_DSP, the DSP fetches the reset interrupt vector at address FF80h and begins the execution of the program code.

information are subject to change.

TI- Proprietary Information – PAGE: 23/51

<sup>\*</sup> CNTL\_RST is a control register mapped in the MCU memory space

# 5. INTERRUPTS MANAGEMENT

->

(level)

#### 5.1 DSP INTERRUPTS

- RSN

- INT0n -

The DSP subchip owns 17 interrupt lines with 11 of which INT0n to INT10n are dedicated for external peripherals. These interrupts are mapped as follows:

reset (HW or SW)

RIF receive interrupt

| - INT1n<br>- INT2n                                                                | (level) -><br>(level) ->                                        | RIF transmit interrupt UART interrupt 1. Error on receiver line. 2. Receive timeout. 3. Received character. 4. Character to transmit. 5. Modem status change. 6. Received XOFF / special character detected. |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                   |                                                                 | 7. CTS/RTS deactivation.                                                                                                                                                                                     |

| - TINT<br>- RINT<br>- RINT<br>- INT3n<br>- INT4n<br>- INT5n<br>- INT6n<br>- INT7n | -><br>-><br>(level) -><br>(level) -><br>(level) -><br>(edge) -> | MCSI DAI interrupt CYPHER interrupts 1. end of ciphering process                                                                                                                                             |

| - INT8n<br>- AINT<br>- INT9n<br>- INT10n<br>- nMIN                                | (edge) -><br>-><br>(edge) -><br>(level) ->                      | <ol> <li>error of processing</li> <li>TPU frame interrupt</li> <li>API interrupts</li> <li>TPU programmable interrupt</li> <li>DMA interrupt</li> <li>Abort on Rhea bus OR INT4n redirection</li> </ol>      |

<u>Note:</u> The TPU programmable interrupt (INT9n) is a facility offered to the DSP programmer in order to allow the generation of a DSP interrupt at a dedicated time with a quarter of GSM bit accuracy. The interrupt is set in a scenario by using a time-stamped instruction.

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

TI- Proprietary Information – PAGE: 24/51

#### 5.2 MCU INTERRUPTS

The ARM7 owns 2 interrupt lines nIRQ and nFIQ. The NAUSICA fast interrupt is mapped on nFIQ

All other peripheral interrupts are mapped on nIRQ as follows:

| Name  | Sense | IRQ      | FIQ      | Function                                                 |

|-------|-------|----------|----------|----------------------------------------------------------|

| IRQ0  | edge  | ✓        |          | Watchdog TIMER interrupts                                |

| IRQ1  | edge  | <b>√</b> |          | TIMER1 interrupt                                         |

| IRQ2  | edge  | ✓        |          | TIMER2 interrupt                                         |

| IRQ3  |       |          | ✓        | TSP receives interrupt                                   |

| IRQ4  | edge  | ✓        |          | TPU frame interrupt                                      |

| IRQ5  | edge  | ✓        |          | TPU page interrupt                                       |

| IRQ6  | edge  | <b>√</b> |          | SIM interrupt                                            |

|       |       |          |          | 1. no answer to reset                                    |

|       |       |          |          | 2. character underflow                                   |

|       |       |          |          | 3. character overflow                                    |

|       |       |          |          | character to transmit                                    |

|       |       |          |          | 5. received character                                    |

|       |       |          |          | 6. SIM card insertion/extraction                         |

| IRQ7  | level | <b>√</b> |          | UART_MODEM interrupts                                    |

|       |       |          |          | error on receiver line                                   |

|       |       |          |          | receive timeout                                          |

|       |       |          |          | received character                                       |

|       |       |          |          | character to transmit                                    |

|       |       |          |          | 5. modem status change                                   |

|       |       |          |          | Received XOFF / special character detected               |

|       |       |          |          | 7. CTS/RTS deactivation                                  |

|       |       |          |          | DSR/RxD activity detection (OFF mode only)               |

| IRQ8  | level | ✓        |          | Keyboard <i>or</i> JogDial interrupt                     |

| IRQ9  | edge  | ✓        |          | RTC periodical timer interrupt                           |

| IRQ10 | level | ✓        |          | RTC ALARM <i>or</i> I2C data transfer error / completion |

| IRQ11 | edge  | ✓        |          | ULPD end of gauging interrupt                            |

| IRQ12 | level | ✓        |          | External interrupt                                       |

| IRQ13 | edge  | ✓        |          | SPI interrupt                                            |

|       |       |          |          | received data                                            |

|       |       |          |          | 2. data to transmit                                      |

| IRQ14 | level | ✓        |          | DMA interrupt                                            |

| IRQ15 | edge  | <b>√</b> |          | API interrupts (nHINT)                                   |

| IRQ16 |       |          | <b>√</b> | SIM card-detect fast interrupt                           |

| IRQ17 |       |          | ✓        | Fast external interrupt                                  |

| IRQ18 | level | ✓        |          | UART_IRDA interrupts                                     |

|       |       |          |          | error on receiver line                                   |

|       |       |          |          | receive timeout                                          |

|       |       |          |          | received character                                       |

|       |       |          |          | character to transmit                                    |

|       |       |          |          | 5. modem status change                                   |

|       |       |          |          | Received XOFF / special character detected               |

|       |       |          |          | 7. CTS/RTS deactivation                                  |

| IRQ19 | level | ✓        |          | ULPD GSM timer                                           |

| IRQ20 | level | ✓        |          | GEA interrupt                                            |

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

TI- Proprietary Information – PAGE: 25/51

**Strictly Private**

UNDER NON DISCLOSURE AGREEMENT

#### 6. DMA MAPPING

The DMA controller is managing the access to the DSP API 6K-word shared memory.

- 1. The MCU ARM7.

- 2. The Radio InterFace (RIF).

- 3. The MODEM UART.

- 4. The IRDA UART.

The RIF-RX and RIF-TX have a dedicated channel each. For UART the following combination are possible:

- ⇒ UART-MODEM have 2 channels:

- ch#2: TX

- ch#3: RX

- ⇒ UART-IRDA have 2 channels:

- ch#2: RX

- ch#3: TX

- □ UART-MODEM and UART-IRDA have one channel each

- ch#2: UART-MODEM

- ch#3: UART-IRDA

RX and/or TX are independently selectable for each module.

- ⇒ UART-MODEM have one channel

- ch#2: RX or TX

- ⇒ UART-IRDA have one channel

- ch#3: RX or TX

- ⇒ UARTs have no DMA.

After reset, all modules have DMA functions disabled.

| DMA request           |   | cha | nnel |   |

|-----------------------|---|-----|------|---|

| DMA request           | 0 | 1   | 2    | 3 |

| RIF_DMA_REQ_X         | ✓ |     |      |   |

| RIF_DMA_REQ_R         |   | ✓   |      |   |

| nDMA_REQ_ARM(0) MODEM |   |     | 1    |   |

| nDMA_REQ_ARM(1) MODEM |   |     |      | ✓ |

| nDMA_REQ_ARM(0) IRDA  |   |     |      | ✓ |

| nDMA_REQ_ARM(1) IRDA  |   |     | 1    |   |

**Table 2: DMA channels allocation**

Note: Only one UART at a time should be allocated to one DMA channel (2 or 3). The potential conflicts between concurrent DMA requests MUST be solved at system level with only one peripheral configured in DMA mode.

information are subject to change.

#### 7. ADDRESS MAPPING

#### 7.1 ARM MEMORY SPACE

ARM memory space is shared between external Memory Interface and RHEA bus. The Memory Interface is providing 6 chip-select signals.

All internal peripherals are mapped on ARM memory space with a range of 32Kbytes.

# 7.1.1 Memory interface: using CS4 (default)

Important: nCS4 is only available from Calypso C035 - F751619

(\*): External memory

| Device name          | nIBOOT | Start address | Stop address | Size (byte) | Data    |  |

|----------------------|--------|---------------|--------------|-------------|---------|--|

| nCS0 (*)             | 1      | 0000:0000     | 003F:FFFF    | 4M          | 8/16/32 |  |

| 11030 ( )            | 0      | 0000:2000     | 003F:FFFF    | 4M – 8K     | 0/10/32 |  |

| nCS6                 | -      | 0080:0000     | 00BF:FFFF    | 512K        | 8/16/32 |  |

| not allocated        | -      | 00C0:0000     | 00FF:FFFF    | -           | -       |  |

| nCS1 (*)             | -      | 0100:0000     | 013F:FFFF    | 4M          | 8/16/32 |  |

| nCS2 (*)             | -      | 0180:0000     | 01BF:FFFF    | 4M          | 8/16/32 |  |

| nCS3 (*)             | -      | 0200:0000     | 023F:FFFF    | 4M          | 8/16/32 |  |

| CS4 (*)              | -      | 0280:0000     | 02BF:FFFF    | 4M          | 8/16/32 |  |

| nCS4 (*)             | -      | 0280:0000     | 02BF:FFFF    | 4M          | 8/16/32 |  |

| nCS0 image           | -      | 0300:0000     | 033F:FFFF    | 4M          | 8/16/32 |  |

| nCS7                 | 1      | 0380:0000     | 03BF:FFFF    | 4M          | 8/16/32 |  |

| 11037                | 0      | 0000:0000     | 0000:1FFF    | 8K          |         |  |

| Debug Unit (DU)      | -      | 03C0:0000     | 03FF:FFFF    | 32          | 32      |  |

| not allocated        | -      | 0400:0000     | FFCF:FFFF    | -           | -       |  |

| API RAM              | -      | FFD0:0000     | FFD0:3FFF    | 16K         | 16/32   |  |

| API control register | -      | FFE0:0000     | FFE0:0001    | 2           | 16      |  |

# 7.1.2 Memory interface: using ADD(22)

Important: nCS4 is only available from Calypso C035 - F751619

(\*): External memory

| Device name          | nIBOOT | Start address | Stop address | Size (byte) | Data    |  |

|----------------------|--------|---------------|--------------|-------------|---------|--|

| nCS0 (*)             | 1      | 0000:0000     | 007F:FFFF    | 8M          | 8/16/32 |  |

| 11030 ( )            | 0      | 0000:2000     | 007F:FFFF    | 8M – 8K     | 0/10/32 |  |

| nCS6                 | -      | 0080:0000     | 00BF:FFFF    | 512K        | 8/16/32 |  |

| not allocated        | -      | 00C0:0000     | 00FF:FFFF    | -           | -       |  |

| nCS1 (*)             | -      | 0100:0000     | 017F:FFFF    | 8M          | 8/16/32 |  |

| nCS2 (*)             | -      | 0180:0000     | 01FF:FFFF    | 8M          | 8/16/32 |  |

| nCS3 (*)             | -      | 0200:0000     | 027F:FFFF    | 8M          | 8/16/32 |  |

| nCS4 (*)             | -      | 0280:0000     | 02BF:FFFF    | 8M          | 8/16/32 |  |

| nCS0 image           | -      | 0300:0000     | 037F:FFFF    | 8M          | 8/16/32 |  |

| nCS7                 | 1      | 0380:0000     | 03FF:FFFF    | 8M          | 8/16/32 |  |

| 11007                | 0      | 0000:0000     | 0000:1FFF    | 8K          | 8/16/32 |  |

| Debug Unit (DU)      | -      | 03C0:0000     | 03FF:FFFF    | 32          | 32      |  |

| not allocated        | -      | 0400:0000     | FFCF:FFFF    | -           | -       |  |

| API RAM              | -      | FFD0:0000     | FFD0:3FFF    | 16K         | 16/32   |  |

| API control register | -      | FFE0:0000     | FFE0:0001    | 2           | 16      |  |

| Debug Unit           | -      |               |              |             |         |  |

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

TI- Proprietary Information – PAGE: 27/51

**Strictly Private**

UNDER NON DISCLOSURE AGREEMENT

# 7.1.3 External Flash/ROM image

In all case and whatever the value of the nIBOOT signal, the external memory mapped on nCS0 is accessible at address defined in nCS0-image range.

Features characteristic data and other information are subject to change.

PAGE: 28/51

**RHEA** peripherals

|                                                                                                                                                                                               | RHEA peripherals                                                       |                                                                                                                                                                                               |                                                                                                                                                                          |                                                                                                                                            |                                                                                                                                                             |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Strobe 0 - Device n                                                                                                                                                                           |                                                                        | Start address                                                                                                                                                                                 | Stop address                                                                                                                                                             | Size in bytes                                                                                                                              | Data                                                                                                                                                        |  |  |

| reserved                                                                                                                                                                                      |                                                                        | FFFF:0000                                                                                                                                                                                     | FFFF:0FFF                                                                                                                                                                | -                                                                                                                                          | -                                                                                                                                                           |  |  |

| TPU registers                                                                                                                                                                                 | CS2                                                                    | FFFF:1000                                                                                                                                                                                     | FFFF:13FF                                                                                                                                                                | 1K                                                                                                                                         | 16                                                                                                                                                          |  |  |

| reserved                                                                                                                                                                                      |                                                                        | FFFF:1400                                                                                                                                                                                     | FFFF:4FFF                                                                                                                                                                | -                                                                                                                                          | -                                                                                                                                                           |  |  |

| UART_IRDA                                                                                                                                                                                     | CS10                                                                   | FFFF:5000                                                                                                                                                                                     | FFFF:57FF                                                                                                                                                                | 2K                                                                                                                                         | 8                                                                                                                                                           |  |  |

| UART_MODEM                                                                                                                                                                                    | CS11                                                                   | FFFF:5800                                                                                                                                                                                     | FFFF:5FFF                                                                                                                                                                | 2K                                                                                                                                         | 8                                                                                                                                                           |  |  |

| UART_MODEM                                                                                                                                                                                    | CS12                                                                   | FFFF:6000                                                                                                                                                                                     | FFFF:67FF                                                                                                                                                                | 2K                                                                                                                                         | 8                                                                                                                                                           |  |  |

| reserved                                                                                                                                                                                      |                                                                        | FFFF:6800                                                                                                                                                                                     | FFFF:6FFF                                                                                                                                                                | -                                                                                                                                          | -                                                                                                                                                           |  |  |

| RIF                                                                                                                                                                                           | CS14                                                                   | FFFF:7000                                                                                                                                                                                     | FFFF:77FF                                                                                                                                                                | 2K                                                                                                                                         | 16                                                                                                                                                          |  |  |

| reserved                                                                                                                                                                                      |                                                                        | FFFF:7800                                                                                                                                                                                     | FFFF:97FF                                                                                                                                                                | -                                                                                                                                          | -                                                                                                                                                           |  |  |

| TPU RAM                                                                                                                                                                                       | CS18                                                                   | FFFF: 9000                                                                                                                                                                                    | FFFF:97FF                                                                                                                                                                | 2K                                                                                                                                         | 16                                                                                                                                                          |  |  |

| DPLL configuration                                                                                                                                                                            | CS19                                                                   | FFFF:9800                                                                                                                                                                                     | FFFF:9801                                                                                                                                                                | 2                                                                                                                                          | 16                                                                                                                                                          |  |  |

| not allocated                                                                                                                                                                                 |                                                                        | FFFF:9802                                                                                                                                                                                     | FFFF:F7FF                                                                                                                                                                | -                                                                                                                                          | -                                                                                                                                                           |  |  |